ASML科技聚焦

在这里,你可以深入探索我们的科技故事,并了解ASML对数字化时代的推动作用和行业价值。

2023-03-30 10:47:00

今天光刻小讲堂在母亲节前夕,来和各位同学一起来看看芯片诞生。芯片的诞生同样也是需要细心的呵护,一步一步地将复杂的电路一层一层地往上叠加制造,最复杂的芯片叠加的层数超过百层。从晶圆裸片到量产芯片出厂,需要超过一个月的时间。其中的环节有任何的差错,就会造成不良芯片甚至整批不良,前功尽弃。

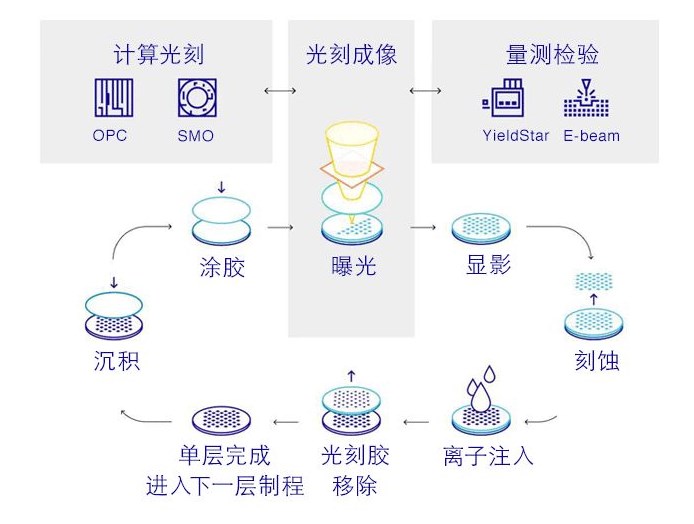

我们来看看芯片制造的关键流程步骤。在上百层的结构中,每一层都包括了从沉积-涂胶-曝光-显影-刻蚀-离子注入-光刻胶移除等重要步骤。那么每一步骤具体在做些什么呢?我们来一步一步看下去。

半导体制造流程

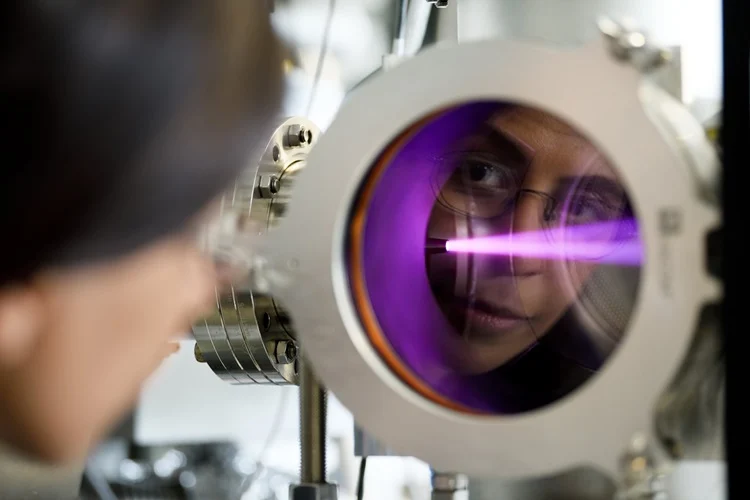

沉积

将硅或是其他材料通过沉积的方式加在晶圆上,作为这一层的基材(基底材料)。并在其上层产生氧化层(二氧化硅)作为绝缘层。

涂胶

将光刻胶均匀旋涂在氧化层(二氧化硅)上。

曝光

使用高能激光透过光罩(reticle)将光罩上的线路图形转移到光刻胶上,光刻胶被激光照射到的部分会产生感光。

显影

加入显影液,将没有被感光的光刻胶溶解去除。此时,氧化层(二氧化硅)上只留下了被感光的光刻胶区域,即光罩上的线路图图形。

刻蚀

使用化学或物理溅射方式将没有被光阻保护的氧化层(二氧化硅)部分去除。

离子注入

在没有被光刻胶或氧化层保护的部分注入离子,在硅层产生半导体层。

光刻胶移除

将多余的光刻胶去除。离子注入之后,已经不再需要光刻胶作为保护层,这时我们就将其除去。

这样,我们就完成了晶圆上单层图形的制作。接下来,我们就重复这样的流程一层一层建构上去。

一开始有和各位同学提到,在这上百层的生产中,其中的环节有任何的差错,就会造成不良芯片甚至整批不良,前功尽弃。而其中最重要的两个指标就是电路线宽(Critical Dimension)的正确性,以及层与层之间套刻精度(Overlay)的准确性。在芯片生产中这两指标主要的掌控点就是在光刻制程。在现在10纳米以下的时代,ASML要如何确保百层生产质量呢?

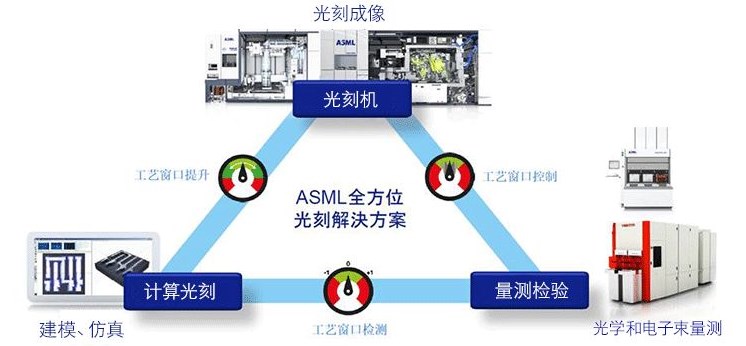

这里就要介绍一下ASML“铁三角”,也就是ASML全方位光刻解决方(ASML Holistic Litho Solution):光刻机、计算光刻、量测检验。

在上一篇小讲堂中也提到,ASML不断在追求摩尔定律的持续实现。而努力的方向就是借由不断地提升分辨率(缩小线宽),来达成在单位面积上可容纳更多的电子组件数目。

然而,随着芯片设计尺寸不断缩小,芯片中最小线宽开始远小于曝光波长,也就越来越逼近光刻投影系统的极限,光的衍射效应变得越来越明显,导致对设计图形产生光学影像退化,实际形成的光刻线路图形相对于光罩上的线路图形发生严重畸变,这种现象称为光学邻近效应(OpticalProximi-ty Effect,OPE)。

而解决的方法就是计算光刻,利用软件和高性能计算,来模拟仿真光刻过程中的光学和化学过程,通过修正光罩的图形设计,来校正光学邻近效应产生的图形畸变。

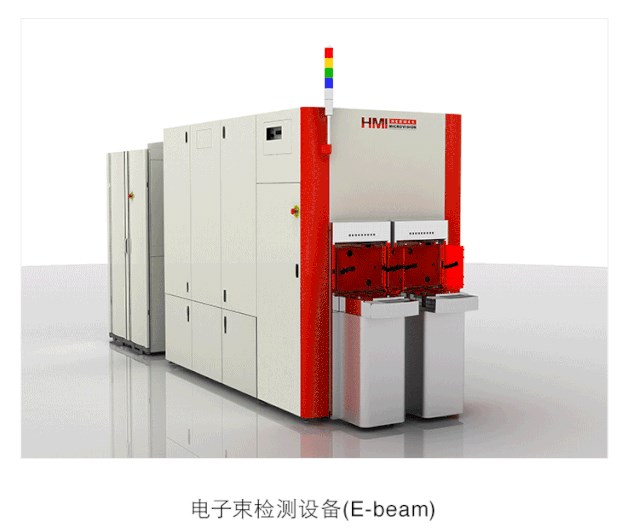

计算光刻站在光刻制程的前端,在设计阶段就针对会产生的图形畸变加以修正。那么在生产过程中呢?在光刻步骤中可能产生的问题,我们要实时地发现并加以修正。这时我们就要来介绍铁三角的另外一角,量测检验。ASML在量测检验主要分二大部分,分别是光学检测设备(YieldStar)和电子束检测设备(E-beam)。

光学检测设备(YieldStar)

量测检验:在晶圆曝光之后,YieldStar可以进行在线实时检测,回馈信号修正光刻机来使曝光的精准度更高,强调实时回馈与修正。而E-beam设备电子束测以聚焦电子束作为检测源,可以捕捉到光学检查设备无法检测到的缺陷,灵敏度高。这两项设备的完美组合确保光刻流程中的缺陷都能被掌握并修正。

现在各位同学都了解到了芯片诞生的过程,每一层每一步骤都是关键。为了生产出良好的芯片,各个环节(从材料、设备、生产到检验)都需要全心投入,保持良好的质量。ASML也不例外,持续以ASML铁三角合作无间,为芯片的发展尽最大的努力。

以上内容均发布在ASML阿斯麦光刻微信公众号,欢迎搜索关注获取更多技术洞察。

;

;

;

;

;

;

;

;